# GLYPH-X

a super regular RISC architecture

January 22, 2026 – v0.6.0-current

**Michael Clark**

Independent Researcher

Maya glyphs in stucco on display at the Museo de Sitio in Palenque, Mexico.

*Image courtesy of Wikipedia. Public domain.*

**to my mentors, whose guidance and wisdom made this work possible.**

---

*"Perfection is achieved,

not when there is nothing more to add,

but when there is nothing left to take away."*

— Antoine de Saint-Exupéry

---

# Contents

|                                                          |           |

|----------------------------------------------------------|-----------|

| <b>Preface</b>                                           | <b>v</b>  |

| <b>1. Architecture</b>                                   | <b>1</b>  |

| 1.1. Introduction . . . . .                              | 1         |

| 1.1.1. load-store . . . . .                              | 2         |

| 1.1.2. registers . . . . .                               | 2         |

| 1.1.3. memory . . . . .                                  | 2         |

| 1.1.4. instructions . . . . .                            | 3         |

| 1.1.5. constants . . . . .                               | 4         |

| 1.2. Program streams . . . . .                           | 5         |

| 1.3. Core concepts . . . . .                             | 6         |

| 1.4. Core parameters . . . . .                           | 7         |

| 1.4.1. architectural parameters . . . . .                | 7         |

| 1.4.2. architectural profiles . . . . .                  | 7         |

| 1.5. Instruction format . . . . .                        | 8         |

| 1.5.1. instruction sizes . . . . .                       | 8         |

| 1.5.2. instruction decoding . . . . .                    | 8         |

| 1.5.3. instruction forms . . . . .                       | 9         |

| 1.6. Register file . . . . .                             | 11        |

| 1.6.1. template architectural profile . . . . .          | 11        |

| 1.6.2. <i>scalar-min</i> architectural profile . . . . . | 12        |

| 1.6.3. <i>scalar-max</i> architectural profile . . . . . | 13        |

| 1.6.4. <i>vector-min</i> architectural profile . . . . . | 14        |

| 1.6.5. <i>vector-max</i> architectural profile . . . . . | 15        |

| 1.7. Example pipeline . . . . .                          | 16        |

| <b>2. System</b>                                         | <b>17</b> |

| 2.1. User-level registers . . . . .                      | 17        |

| 2.1.1. floating-point unit registers . . . . .           | 18        |

| 2.1.2. clock and frequency registers . . . . .           | 19        |

| 2.1.3. thread address registers . . . . .                | 19        |

| 2.2. System registers . . . . .                          | 20        |

| 2.2.1. privileged trap registers . . . . .               | 21        |

| 2.2.2. privileged system registers . . . . .             | 24        |

| 2.2.3. privileged debug registers . . . . .              | 27        |

| 2.3. Capability extension . . . . .                      | 29        |

| 2.3.1. capability control registers . . . . .            | 30        |

|                                                  |           |

|--------------------------------------------------|-----------|

| 2.3.2. capability permission registers . . . . . | 30        |

| 2.3.3. capability role registers . . . . .       | 31        |

| 2.3.4. capability matrix registers . . . . .     | 32        |

| 2.4. Domain extension . . . . .                  | 33        |

| 2.4.1. domain control registers . . . . .        | 34        |

| 2.4.2. domain routing registers . . . . .        | 35        |

| 2.4.3. domain context registers . . . . .        | 36        |

| 2.5. Machine extension . . . . .                 | 37        |

| 2.5.1. machine control registers . . . . .       | 38        |

| 2.5.2. machine memory registers . . . . .        | 39        |

| 2.6. Environment extension . . . . .             | 40        |

| 2.6.1. environment control registers . . . . .   | 41        |

| 2.7. Address translation . . . . .               | 42        |

| 2.7.1. page table structure . . . . .            | 42        |

| 2.7.2. page table entries . . . . .              | 42        |

| 2.7.3. page table addresses . . . . .            | 43        |

| 2.7.4. page table translation . . . . .          | 43        |

| <b>3. Instructions</b>                           | <b>45</b> |

| 3.1. Instruction listing — 16-bit . . . . .      | 45        |

| 3.1.1. break . . . . .                           | 45        |

| 3.1.2. j . . . . .                               | 45        |

| 3.1.3. b . . . . .                               | 45        |

| 3.1.4. ibj . . . . .                             | 46        |

| 3.1.5. link . . . . .                            | 46        |

| 3.1.6. movh . . . . .                            | 47        |

| 3.1.7. movw . . . . .                            | 47        |

| 3.1.8. movi . . . . .                            | 47        |

| 3.1.9. addi . . . . .                            | 47        |

| 3.1.10. srli . . . . .                           | 48        |

| 3.1.11. srai . . . . .                           | 48        |

| 3.1.12. slli . . . . .                           | 48        |

| 3.1.13. addh . . . . .                           | 48        |

| 3.1.14. leapc . . . . .                          | 49        |

| 3.1.15. loadpc . . . . .                         | 49        |

| 3.1.16. storepc . . . . .                        | 49        |

| 3.1.17. load . . . . .                           | 49        |

| 3.1.18. store . . . . .                          | 50        |

| 3.1.19. compare . . . . .                        | 50        |

| 3.1.20. logic . . . . .                          | 51        |

| 3.1.21. pin . . . . .                            | 51        |

| 3.1.22. and . . . . .                            | 52        |

| 3.1.23. or . . . . .                             | 52        |

| 3.1.24. xor . . . . .                            | 52        |

## *Contents*

|                                              |           |

|----------------------------------------------|-----------|

| 3.1.25. add . . . . .                        | 52        |

| 3.1.26. srl . . . . .                        | 53        |

| 3.1.27. sra . . . . .                        | 53        |

| 3.1.28. sll . . . . .                        | 53        |

| 3.1.29. sub . . . . .                        | 53        |

| 3.1.30. mul . . . . .                        | 54        |

| 3.1.31. div . . . . .                        | 54        |

| 3.1.32. illegal . . . . .                    | 54        |

| <b>4. Assembly</b>                           | <b>55</b> |

| 4.1. Introduction . . . . .                  | 55        |

| 4.2. Concepts . . . . .                      | 55        |

| 4.2.1. assembly . . . . .                    | 55        |

| 4.2.2. object . . . . .                      | 55        |

| 4.2.3. archive . . . . .                     | 55        |

| 4.2.4. executable . . . . .                  | 55        |

| 4.2.5. shared library . . . . .              | 56        |

| 4.2.6. section . . . . .                     | 56        |

| 4.2.7. segment . . . . .                     | 56        |

| 4.2.8. symbol . . . . .                      | 56        |

| 4.2.9. relocation . . . . .                  | 56        |

| 4.2.10. program linking . . . . .            | 56        |

| 4.3. Directives . . . . .                    | 57        |

| 4.4. Pseudo-instructions . . . . .           | 58        |

| 4.5. Calling convention . . . . .            | 59        |

| 4.5.1. calling convention — 16-bit . . . . . | 59        |

| <b>A. Appendix</b>                           | <b>60</b> |

| A.1. Opcode summary — 16-bit . . . . .       | 60        |

| <b>References</b>                            | <b>61</b> |

# Preface

this document introduces a RISC architecture designed with simplicity as its dominating principle, along with several features not yet present in mainstream RISC architectures:

- a compression technique for split instruction and constant streams.

- a variable-length instruction format designed for vectorized decoding.

- an efficient frontier between hardware synthesis and software translation.

- a modern approach to virtualization, memory management, and capabilities.

the document begins with a general introduction to RISC architectures, including principal elements such as load-store operation, memory, registers, instructions, and constants. it then presents an overview of the proposed architecture, followed by sections on program streams, the variable-length instruction format, the instruction set, its assembly syntax, and the programming language calling convention.

this document does not simply present an architecture reimplementing existing ideas; rather, it introduces a novel architecture featuring an instruction coding scheme optimized for efficient parallel decoding in hardware or software, combined with contemporary practices in instruction semantics, including the use of single-bit predicates for compare, divide, branch, plus arithmetic instructions with carry, to achieve an optimal mapping to vectors.

in addition to the core instruction set, the architecture also defines extensions for capabilities, virtual domains, software-defined memory management and environment. the capability extension adds fine-grained page-based permissions and role based access control. the domain extension adds virtualization for trap routing, page translation, and context switching. the machine extension provides for custom address translation schemes. finally, the environment extension adds controls for power and reset.

this work is intended for computer architects, systems programmers, students of computing machinery, and anyone interested in the evolution of RISC design. by the end of the document, readers should be able to reason about computer programs at the instruction level and understand the logic behind the architecture's design choices—with enough detail to implement the architecture in hardware or software.

# 1. Architecture

## 1.1. Introduction

this section gives a brief introduction to RISC architectures.

A RISC<sup>1</sup> machine is a type of general-purpose computer with the characteristic that it has a reduced set of instructions in contrast to a CISC<sup>2</sup> machine. A RISC machine is Turing complete meaning it can perform any computation that a Turing machine can, given enough time and memory. a Turing machine [12] is a theoretical model of computation.

a RISC machine has a set of instructions which comprise basic operations such as: *load-from-memory*, *store-to-memory*, *add*, *subtract*, *compare*, plus *conditional branch* and *unconditional branch* instructions et cetera; which one can imagine as a list of instructions on a paper tape. each instruction has an *opcode*, which is a unique binary pattern that identifies the *operation*, plus several *operands*, which are arguments to the instruction.

```

register-0 = load-from-memory at tape-address-0

register-1 = load-from-memory at tape-address-1

register-2 = add register-0 and register-1

store-to-memory register-2 at tape-address-2

```

some instructions have operands that point to values inside of *registers* in a *register-file* which is like a close filing cabinet containing cards with numbers on them, and some of these numbers are addresses that point to values in *main-memory* which is like a larger but slower filing cabinet. some of these values are *immediate* values which are small numbers listed inside of the instructions on the paper tape.

the paper tape is just a way conceptualize a list of instructions stored in *main-memory*. there is a special register called *PC* short for *program counter*, which points to the current position on the tape. after each instruction executes the tape is advanced to the next instruction and the *program counter* is incremented, until it encounters a *branch* instruction which causes it to move forwards or backwards to a different position on the tape. branch instructions can be *conditional* or *unconditional*. conditional branches are selectively executed based on the results of a comparison instruction.

---

<sup>1</sup>Reduced Instruction Set Computer

<sup>2</sup>Complex Instruction Set Computer

## 1. Architecture

### 1.1.1. load-store

a *load-store* architecture [4] is a way to characterize RISC architectures where most instructions have simple operands that point to values held in registers, plus *load* and *store* instructions to retrieve and commit values to main memory. a *load-store* architecture alleviates the need to add complex addressing modes, plus intput-output to peripherals and secondary storage use *MMIO*<sup>3</sup> to avoid needing special *Input/Output* instructions.

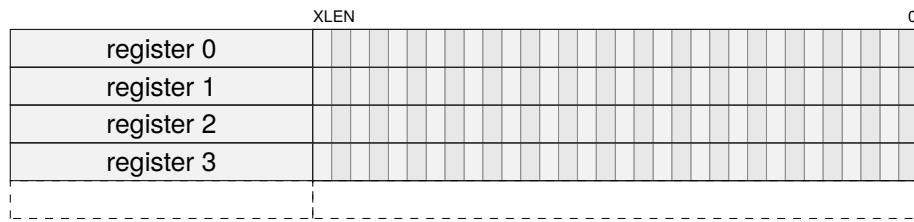

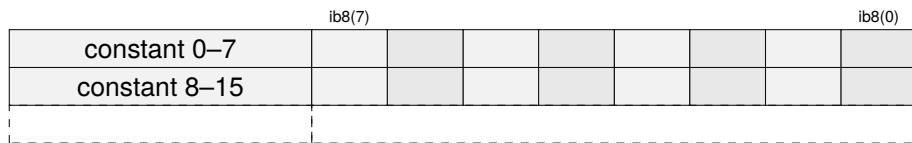

### 1.1.2. registers

registers are temporary storage used to fill input and output operands for the *ALU*<sup>4</sup> before and after execution of instructions. registers are organized as a word-addressable store where each register number refers to  $XLEN \in \{64, 128\}$  bits of data.  $XLEN$  is a parameter that specifiess the width of registers in bits.

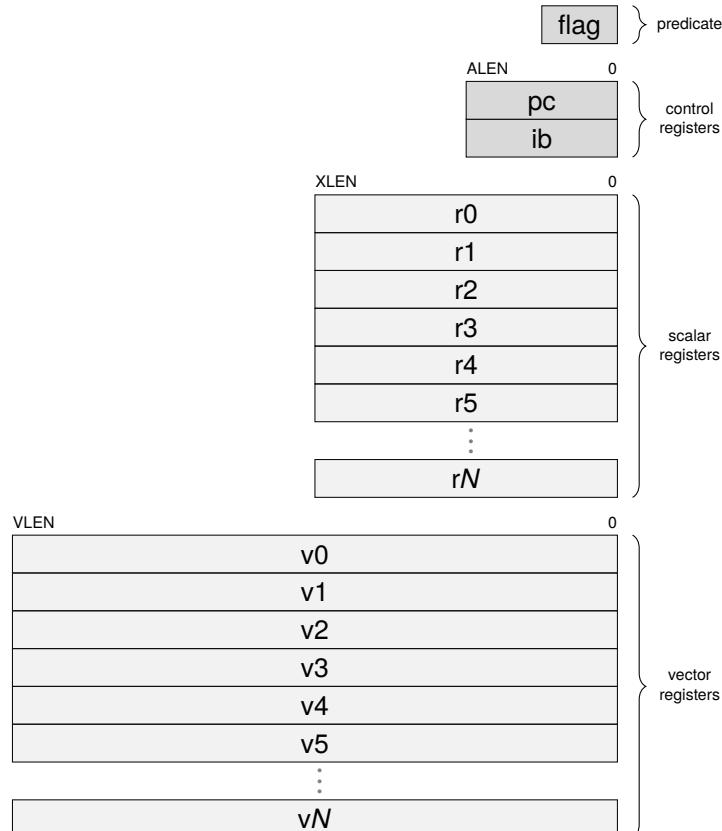

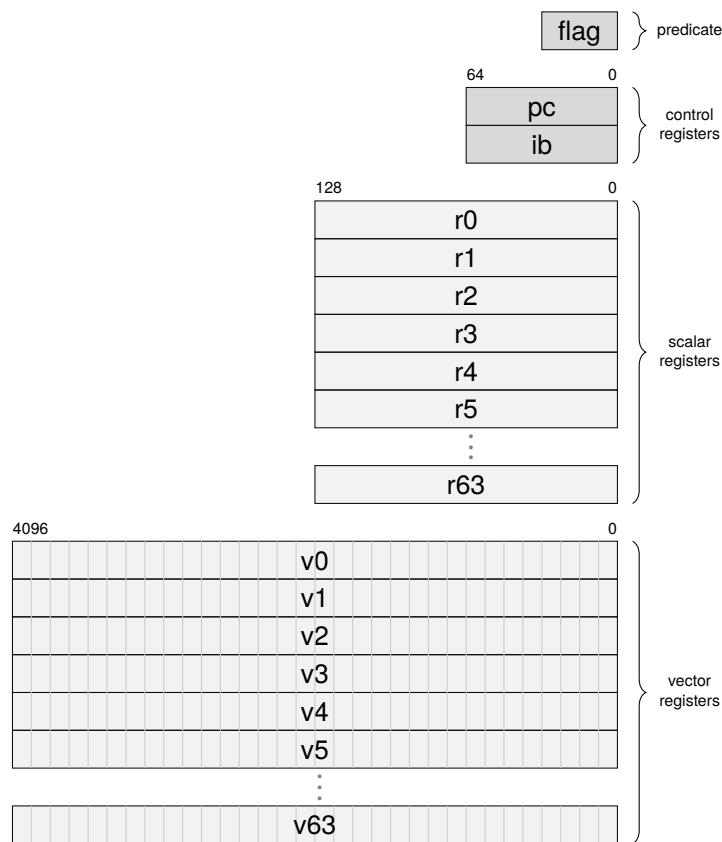

Figure 1.1.: organization of register storage.

### 1.1.3. memory

main memory is primary storage which in modern computers is most likely *DRAM*<sup>5</sup>. main memory is organized as a byte-addressable store where each address refers to a byte which is 8-bits of data.  $ALEN$  is a parameter that specifies the width of addresses in bits.

Figure 1.2.: organization of main-memory storage.

---

<sup>3</sup>MMIO - Memory-mapped I/O.

<sup>4</sup>ALU – Arithmetic logic unit.

<sup>5</sup>DRAM – Dynamic random-access memory.

## 1. Architecture

#### 1.1.4. instructions

instruction memory is a memory region dedicated to program instructions. it is organized as a word-addressable store, similar to main memory, but is read-only and reserved exclusively for instructions. this configuration is typically referred to as a Harvard architecture [1], in contrast to a Von Neumann architecture [9], which uses a shared memory region for both program instructions and data.

instruction words contain packets of 16-bits which are composed of size, opcode, and operand fields. instruction packets can be appended together to form larger instruction words with larger opcode and operand fields. section 1.5 provides details on the instruction template and instruction forms.

|                   |   |                  |   |              |

|-------------------|---|------------------|---|--------------|

| 15                | 7 | 6                | 2 | 1 0          |

| $operand_{[8:0]}$ |   | $opcode_{[4:0]}$ |   | $sz_{[1:0]}$ |

Figure 1.3.: 16-bit instruction containing one packet.

|                    |   |                  |   |              |   |

|--------------------|---|------------------|---|--------------|---|

| 15                 | 7 | 6                | 2 | 1            | 0 |

| $operand_{[8:0]}$  |   | $opcode_{[4:0]}$ |   | $sz_{[1:0]}$ |   |

| $operand_{[17:9]}$ |   | $opcode_{[9:5]}$ |   | $sz_{[3:2]}$ |   |

Figure 1.4.: 32-bit instruction containing two packets.

instruction words are packed together into instruction blocks containing instruction size information that is used to fuse them together to compose variable-length instructions [8]. instruction words can begin on any 16-bit aligned address. instruction memory is addressed with displacements from the *program counter* called *pc-relative* addresses.

|                 | pcrel(3) |  |  |  | pcrel(0) |

|-----------------|----------|--|--|--|----------|

| instruction 0–3 |          |  |  |  |          |

| instruction 4–7 |          |  |  |  |          |

Figure 1.5.: organization of instruction-memory with 16-bit instructions.

The diagram illustrates a memory layout for a pcrel(3) instruction. It consists of two rows. The top row is labeled "pcrel(3)" and the bottom row is labeled "pcrel(0)". The first row contains the text "instruction 0-3" and the second row contains "instruction 4-7". A horizontal arrow points from the end of the first row to the start of the second row, indicating a relative offset. The first row is shaded grey, and the second row is white.

Figure 1.6.: organization of instruction-memory with 16-bit and 32-bit instructions.

## 1. Architecture

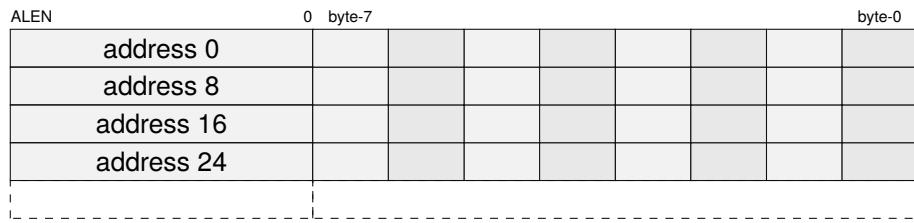

### 1.1.5. constants

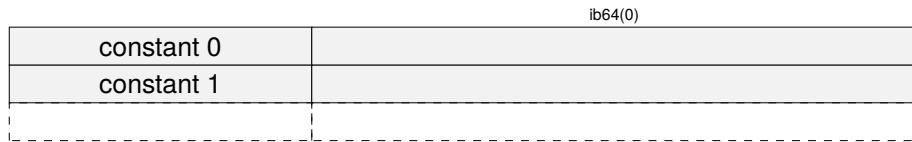

constant memory [11] is a memory region dedicated to constants. it is organized as a word-addressable store like main-memory, but is read-only and restricted to constants. instructions can refer to constants using *ib-relative* addresses inside instruction operands. section 1.2 provides more details on the split instruction and constant streams.

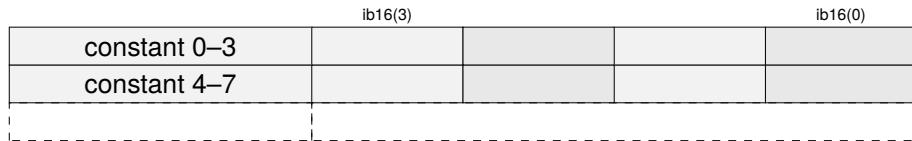

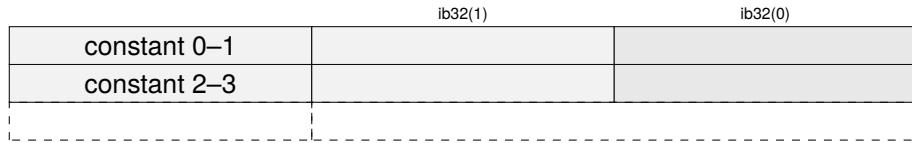

constant memory is addressed with displacements from the *immediate base* register called *ib-relative* addresses which are stored inside instruction operand slots, are sized, scaled and aligned addresses computed relative to the *immediate base* register, which is like a program counter for constants. these diagrams show  $ib8(n)$  through  $ib64(n)$  *ib-relative* addresses for access to 8-bit through to 64-bit constants respectively: *note: ib-relative addresses alias a single constant storage space containing all types.*

Figure 1.7.: organization of  $ib8$  constant-memory storage.

Figure 1.8.: organization of  $ib16$  constant-memory storage.

Figure 1.9.: organization of  $ib32$  constant-memory storage.

Figure 1.10.: organization of  $ib64$  constant-memory storage.

## 1.2. Program streams

glyph separates the stored programs into two streams, one with instructions and one with constants [11]. the instruction stream is addressed with the *program counter* (*pc*) and the constant stream is addressed with the *immediate base* (*ib*) register. this could be referred to as split program stream Harvard architecture.

Figure 1.11.: program counter and immediate base register.

instruction blocks are aligned memory blocks addressed by the *program counter*. instruction memory is addressed with *pc-relative* addresses in instruction immediate values or indirectly with constants accessed using *ib-relative* addresses stored inside instruction operand slots.

immediate blocks are aligned memory blocks addressed by the *immediate base* register. constant memory is addressed with *ib-relative* addresses stored inside instruction operand slots, which are sized, scaled, and aligned relative to the *immediate base* register.

the constant stream branches independently using the *immediate-block-jump* instruction to update the *immediate base* register, or together with the *program counter* in procedure call and return instructions that branch instruction and constants at the same time; *jump-and-link-immediate-block* and *jump-to-link-immediate-block* add and subtract address vectors to  $(pc, ib)$ . the *pack-indirect* instruction allows absolute  $(pc, ib)$  addresses to be packed into an address vector for indirect calls.

the instruction forms use bonded operand slots for immediate operands and operand bits do not overlap opcode bits. the use of immediate blocks means large immediate constants can all be accessed using short references encoded inside of operand slots for instructions that use an immediate block relative addressing mode.

### 1.3. Core concepts

glyph is a super regular RISC architecture that encodes constants in a secondary stream accessed via an *immediate base* register that points at immediate blocks containing constants accessed via a constant address mode. the *immediate base* register branches like the *program counter*, and procedure calls and returns set and restore  $(pc,ib)$  together.

glyph uses relative address vectors in its link register which is different to typical RISC architectures. glyph does this so that the branch instructions can fit  $(pc,ib)$  into the a single link register for compatibility with traditional RISC architectures. glyph achieves this by packing two relative  $(pc,ib)$  displacements into a relative address vector<sup>6</sup>.

immediate blocks can be switched using the immediate block branch instruction. immediate blocks, unlike typical RISC architectures, mean that most relocations are word sized like CISC architectures, and can use C-style structure packing and alignment rules.

this list outlines some differentiating elements of the super regular RISC architecture:

- variable length instruction format supporting 16, 32, and 64-bit instructions.

- 1-bit predicate for compare, branch, add with carry, and subtract with borrow.

- 16-bit compressed instruction packets that can access 8 registers.

- $(pc,ib)$  is a *program counter* and *immediate base* register address vector.

- link register contains a packed relative  $(pc,ib)$  address vector to function entry.

- *ibj* — *immediate-block-jump* adds a relative address to the *immediate base* register.

- *movw* — *move-word-immediate-block* uses a displacement to access a constant.

- *jalib* — *jump-and-link-immediate-block* or *link-function-call* copies the address vector into the link register and adds constants to  $(pc,ib)$ . it is used to branch the *program counter* and *immediate base* register at the same time for calling procedures.

- *jilib* — *jump-to-link-immediate-block* or *link-function-return* subtracts link vector from and adds constants to  $(pc,ib)$ . it is used to branch the *program counter* and the *immediate base* register at the same time for returning from called procedures.

- *pin* — *pack-indirect* packs two absolute addresses as relative address vector from  $(pc,ib)$  and is used for calling absolute addresses such as virtual functions.

the *pin* and *link* instructions form a modular arithmetic ring of relative address vectors, due to their use of relative addresses. relative address vectors can be encrypted, decrypted, and authenticated to form a verifiable chain of addresses for control flow integrity.

---

<sup>6</sup>the architecture defines two parameters: *ALEN* and *XLEN*, which respectively to refer to width of addresses and width of general purpose registers in bits. when  $XLEN \geq ALEN \times 2$  it is possible to pack absolute addresses instead of relative addresses, as would be the case where *ALEN*=64 and *XLEN*=128.

## 1.4. Core parameters

glyph has several architectural parameters that define the dimensions of an instance of the architecture to allow the architecture to be instantiated in several different configurations. these configurations are grouped into architectural profiles.

### 1.4.1. architectural parameters

glyph defines a unified floating-point and integer scalar register file with 8 or 64 registers and an optional unified floating-point and integer vector register file with 64 registers.

- 16-bit instruction packet can access 8 registers with up to 3 operands.

- 32-bit instruction packet can access 64 registers with up to 3 operands.

- 64-bit instruction packet can access 64 registers with up to 6 operands.

glyph architectural parameters are as follows:

| Parameter | Value      | Description                            |

|-----------|------------|----------------------------------------|

| SREG      | 8, 64      | number of scalar registers             |

| VREG      | -, 64      | number of vector registers             |

| ILEN      | 16, 32, 64 | width of largest instruction in bits   |

| ALEN      | 64         | width of arithmetic on scalars in bits |

| XLEN      | 64, 128    | width of scalar registers in bits      |

| VLEN      | 512, 4096  | width of vector registers in bits      |

| GLEN      | 128        | width of vector lane group in bits     |

Table 1.1.: architectural parameters

### 1.4.2. architectural profiles

glyph architectural parameters are linked to the dimensions of the register slots in the variable length instruction packets. the 16-bit packet can be used in a freestanding microcontroller profile. the 32-bit packet contains scalar and packed-SIMD<sup>7</sup> instructions on scalar registers. the 64-bit packet contains packed-SIMD instruction on vector registers.

| profile    | SREG | VREG | ILEN | ALEN | XLEN | VLEN | GLEN |

|------------|------|------|------|------|------|------|------|

| scalar-min | 8    | -    | 16   | 64   | 64   | -    | -    |

| scalar-max | 64   | -    | 32   | 64   | 128  | -    | -    |

| vector-min | 64   | 64   | 64   | 64   | 128  | 512  | 128  |

| vector-max | 64   | 64   | 64   | 64   | 128  | 4096 | 128  |

Table 1.2.: architectural profiles

<sup>7</sup>SIMD - Single Instruction Multiple Data

## 1. Architecture

### 1.5. Instruction format

instructions use a variable length format [8] with a 16-bit instruction packet that supports 16, 32, 64, and 128-bit instruction words. the instruction packet uses a *super regular* scheme, whereby successive instruction packets extend the fields in the previous instruction packet [7]. instruction words can begin on any 16-bit aligned address.

#### 1.5.1. instruction sizes

the variable length instruction format has a *2-bit* size field inspired by LEB128 [5] in a fixed position in every instruction packet, to reduce the complexity of size-decoding for variable length instructions<sup>8</sup>. this table shows the size fields for the different instruction sizes:

| Instruction size | Size vector      |

|------------------|------------------|

| 16-bit           | {00}             |

| 32-bit           | {01, 11}         |

| 64-bit           | {10, 11, 11, 11} |

Table 1.3.: variable-length instruction size fields

#### 1.5.2. instruction decoding

the instruction size encoding and field extension scheme has been designed to minimize complexity for parallel decoding in hardware and software. the following table shows the instruction width combinations for various width parallel instruction decoders.

| Packets | Bits    | Bytes | $n_{combinations}$ | $\log_2(n)$ |

|---------|---------|-------|--------------------|-------------|

| 1-wide  | 16-bit  | 2     | 1                  | 0           |

| 2-wide  | 32-bit  | 4     | 16                 | 4           |

| 4-wide  | 64-bit  | 8     | 58                 | 5.86        |

| 8-wide  | 128-bit | 16    | 574                | 9.16        |

| 16-wide | 256-bit | 32    | 51904              | 15.66       |

Table 1.4.: instruction decode combinations

---

<sup>8</sup>instructions are considered *well-formed* if the size field of subsequent packets has the value 11.

## 1. Architecture

### 1.5.3. instruction forms

the variable length instruction format has a single base format where fields in the template instruction form are extended by successive instruction packets.

the instructions forms are super regular in that operand and opcode bits do not overlap and the number and complexity of the formats is reduced so that vectorized instruction decoding is simple in both hardware and software. the scheme is designed so that *1-bit* of coding space in the larger packet can be used to extend register sizes.

### instruction templates

this section details the layout of the variable sized instructions:

|    |   |                                   |                                  |                            |                                          |

|----|---|-----------------------------------|----------------------------------|----------------------------|------------------------------------------|

| 15 | 7 | 6                                 | 2                                | 1 0                        | <b>op16</b><br>16-bit instruction packet |

|    |   | <i>operand</i> <sub>[8:0]</sub>   | <i>opcode</i> <sub>[4:0]</sub>   | <i>sz</i> <sub>[1:0]</sub> |                                          |

| 15 | 7 | 6                                 | 2                                | 1 0                        | <b>op32</b><br>32-bit instruction packet |

|    |   | <i>operand</i> <sub>[8:0]</sub>   | <i>opcode</i> <sub>[4:0]</sub>   | <i>sz</i> <sub>[1:0]</sub> |                                          |

|    |   | <i>operand</i> <sub>[17:9]</sub>  | <i>opcode</i> <sub>[9:5]</sub>   | <i>sz</i> <sub>[3:2]</sub> |                                          |

| 15 | 7 | 6                                 | 2                                | 1 0                        | <b>op64</b><br>64-bit instruction packet |

|    |   | <i>operand</i> <sub>[8:0]</sub>   | <i>opcode</i> <sub>[4:0]</sub>   | <i>sz</i> <sub>[1:0]</sub> |                                          |

|    |   | <i>operand</i> <sub>[17:9]</sub>  | <i>opcode</i> <sub>[9:5]</sub>   | <i>sz</i> <sub>[3:2]</sub> |                                          |

|    |   | <i>operand</i> <sub>[26:18]</sub> | <i>opcode</i> <sub>[14:10]</sub> | <i>sz</i> <sub>[5:4]</sub> |                                          |

|    |   | <i>operand</i> <sub>[35:27]</sub> | <i>opcode</i> <sub>[19:15]</sub> | <i>sz</i> <sub>[7:6]</sub> |                                          |

### 16-bit instruction forms

this section details the layout of the 16-bit instruction forms:

|                            |                            |                             |                                                     |           |                                                    |

|----------------------------|----------------------------|-----------------------------|-----------------------------------------------------|-----------|----------------------------------------------------|

| 15                         | 7                          | 6                           | 2                                                   | 1 0       | <b>op16i</b><br>16-bit large immediate             |

|                            |                            | <i>imm</i> <sub>[5:0]</sub> | <i>opcode</i> <sub>[4:0]</sub>                      | <b>00</b> |                                                    |

| 15 13 12                   | 7                          | 6                           | 2                                                   | 1 0       | <b>op16ri</b><br>16-bit one operand with immediate |

| <i>rc</i> <sub>[2:0]</sub> |                            | <i>imm</i> <sub>[5:0]</sub> | <i>opcode</i> <sub>[4:0]</sub>                      | <b>00</b> |                                                    |

| 15 13 12 10 9 7 6          | 2                          | 1 0                         | <b>op16rri</b><br>16-bit two operand with immediate |           |                                                    |

| <i>rc</i> <sub>[2:0]</sub> | <i>rb</i> <sub>[2:0]</sub> | <i>imm</i> <sub>[2:0]</sub> | <i>opcode</i> <sub>[4:0]</sub>                      | <b>00</b> |                                                    |

| 15 13 12 10 9 7 6          | 2                          | 1 0                         | <b>op16r3</b><br>16-bit three operand               |           |                                                    |

| <i>rc</i> <sub>[2:0]</sub> | <i>rb</i> <sub>[2:0]</sub> | <i>ra</i> <sub>[2:0]</sub>  | <i>opcode</i> <sub>[4:0]</sub>                      | <b>00</b> |                                                    |

## 1. Architecture

### 32-bit instruction forms

this section details the layout of the 32-bit instruction forms:

|                |   |                  |   |           |

|----------------|---|------------------|---|-----------|

| 15             | 7 | 6                | 2 | 1 0       |

| $imm_{[8:0]}$  |   | $opcode_{[4:0]}$ |   | <b>01</b> |

| $imm_{[17:9]}$ |   | $opcode_{[9:5]}$ |   | <b>11</b> |

**op32i**

32-bit large immediate

|              |    |                |   |                  |           |

|--------------|----|----------------|---|------------------|-----------|

| 15 13        | 12 | 7              | 6 | 2                | 1 0       |

| $rc_{[2:0]}$ |    | $imm_{[5:0]}$  |   | $opcode_{[4:0]}$ | <b>01</b> |

| $rc_{[5:3]}$ |    | $imm_{[11:6]}$ |   | $opcode_{[9:5]}$ | <b>11</b> |

**op32ri**

32-bit one operand with immediate

|              |              |               |   |                  |           |

|--------------|--------------|---------------|---|------------------|-----------|

| 15 13        | 12 10        | 9 7           | 6 | 2                | 1 0       |

| $rc_{[2:0]}$ | $rb_{[2:0]}$ | $imm_{[2:0]}$ |   | $opcode_{[4:0]}$ | <b>01</b> |

| $rc_{[5:3]}$ | $rb_{[5:3]}$ | $imm_{[5:3]}$ |   | $opcode_{[9:5]}$ | <b>11</b> |

**op32rri**

32-bit two operand with immediate

|              |              |              |   |                  |           |

|--------------|--------------|--------------|---|------------------|-----------|

| 15 13        | 12 10        | 9 7          | 6 | 2                | 1 0       |

| $rc_{[2:0]}$ | $rb_{[2:0]}$ | $ra_{[2:0]}$ |   | $opcode_{[4:0]}$ | <b>01</b> |

| $rc_{[5:3]}$ | $rb_{[5:3]}$ | $ra_{[5:3]}$ |   | $opcode_{[9:5]}$ | <b>11</b> |

**op32r3**

32-bit three operand

### 64-bit instruction forms

this section details the layout of the 64-bit instruction forms:

|                 |   |                    |   |           |

|-----------------|---|--------------------|---|-----------|

| 15              | 7 | 6                  | 2 | 1 0       |

| $imm_{[5:0]}$   |   | $opcode_{[4:0]}$   |   | <b>10</b> |

| $imm_{[11:6]}$  |   | $opcode_{[9:5]}$   |   | <b>11</b> |

| $imm_{[17:12]}$ |   | $opcode_{[14:10]}$ |   | <b>11</b> |

| $imm_{[23:18]}$ |   | $opcode_{[19:15]}$ |   | <b>11</b> |

**op64i**

64-bit large immediate

|               |    |                 |   |                    |           |

|---------------|----|-----------------|---|--------------------|-----------|

| 15 13         | 12 | 7               | 6 | 2                  | 1 0       |

| $rc_{[2:0]}$  |    | $imm_{[5:0]}$   |   | $opcode_{[4:0]}$   | <b>10</b> |

| $rc_{[5:3]}$  |    | $imm_{[11:6]}$  |   | $opcode_{[9:5]}$   | <b>11</b> |

| $rf_{[8:6]}$  |    | $imm_{[17:12]}$ |   | $opcode_{[14:10]}$ | <b>11</b> |

| $rf_{[11:9]}$ |    | $imm_{[23:18]}$ |   | $opcode_{[19:15]}$ | <b>11</b> |

**op64rri**

64-bit two operand with immediate

|               |               |                |   |                    |           |

|---------------|---------------|----------------|---|--------------------|-----------|

| 15 13         | 12 10         | 9 7            | 6 | 2                  | 1 0       |

| $rc_{[2:0]}$  | $rb_{[2:0]}$  | $imm_{[2:0]}$  |   | $opcode_{[4:0]}$   | <b>10</b> |

| $rc_{[5:3]}$  | $rb_{[5:3]}$  | $imm_{[5:3]}$  |   | $opcode_{[9:5]}$   | <b>11</b> |

| $rf_{[8:6]}$  | $re_{[8:6]}$  | $imm_{[8:6]}$  |   | $opcode_{[14:10]}$ | <b>11</b> |

| $rf_{[11:9]}$ | $re_{[11:9]}$ | $imm_{[11:9]}$ |   | $opcode_{[19:15]}$ | <b>11</b> |

**op64r4i**

64-bit four operand with immediate

|               |               |               |   |                    |           |

|---------------|---------------|---------------|---|--------------------|-----------|

| 15 13         | 12 10         | 9 7           | 6 | 2                  | 1 0       |

| $rc_{[2:0]}$  | $rb_{[2:0]}$  | $ra_{[2:0]}$  |   | $opcode_{[4:0]}$   | <b>10</b> |

| $rc_{[5:3]}$  | $rb_{[5:3]}$  | $ra_{[5:3]}$  |   | $opcode_{[9:5]}$   | <b>11</b> |

| $rf_{[8:6]}$  | $re_{[8:6]}$  | $rd_{[8:6]}$  |   | $opcode_{[14:10]}$ | <b>11</b> |

| $rf_{[11:9]}$ | $re_{[11:9]}$ | $rd_{[11:9]}$ |   | $opcode_{[19:15]}$ | <b>11</b> |

**op64r6**

64-bit six operand

## 1.6. Register file

glyph has register state comprised of a predicate register, program counter, and immediate base registers, a unified floating-point and integer scalar register file, and an optional unified floating-point and integer vector register file, each with an extensible number of registers.

### 1.6.1. template architectural profile

the register state accessible by the template architectural profile is comprised of:

- 1-bit predicate register (*flag*).

- ALEN-bit *program counter* register (aligned to 2 bytes).

- ALEN-bit *immediate base* register (aligned to 64 bytes).

- SREG  $\times$  XLEN-bit scalar registers (r0 — rN).

- VREG  $\times$  VLEN-bit vector registers (v0 — vN).

the following diagram shows the template architectural profile register state:

Figure 1.12.: template architectural profile register state.

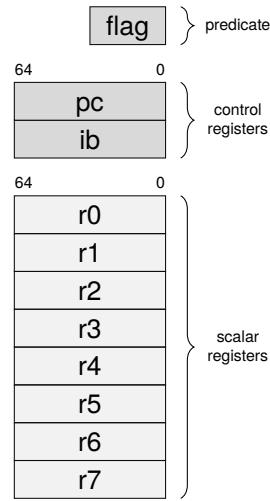

### 1.6.2. *scalar-min* architectural profile

the register state accessible by the *scalar-min* architectural profile is comprised of:

- 1-bit predicate register (*flag*).

- 64-bit *program counter* register (aligned to 2 bytes).

- 64-bit *immediate base* register (aligned to 64 bytes).

- $8 \times 64$ -bit scalar registers ( $r0 — r7$ ).

the following diagram shows the *scalar-min* architectural profile register state:

Figure 1.13.: *scalar-min* architectural profile register state.

when  $XLEN < ALEN \times 2$  it is not possible to pack absolute addresses in the link register, so the PIN and LINK instructions save relative addresses in the link register. this increases latency in branch address calculation compared to absolute addresses.

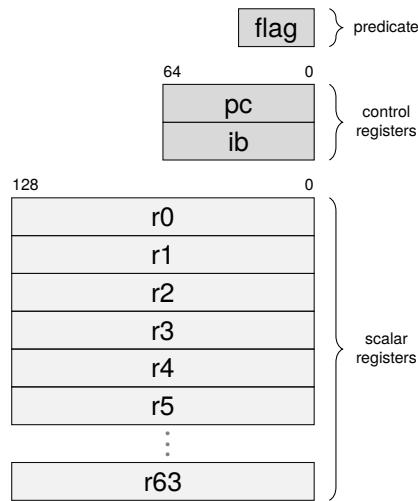

### 1.6.3. *scalar-max* architectural profile

the register state accessible by the *scalar-max* architectural profile is comprised of:

- 1-bit predicate register (*flag*).

- 64-bit *program counter* register (aligned to 2 bytes).

- 64-bit *immediate base* register (aligned to 64 bytes).

- $64 \times 128$ -bit scalar registers ( $r0 — r63$ ).

the following diagram shows the *scalar-max* architectural profile register state:

Figure 1.14.: *scalar-max* architectural profile register state.

when  $XLEN \geq ALEN \times 2$  it is possible to pack absolute addresses in the link register, so the PIN and LINK instructions save absolute addresses in the link register instead. this reduces latency in branch address calculation compared to relative addresses.

## 1. Architecture

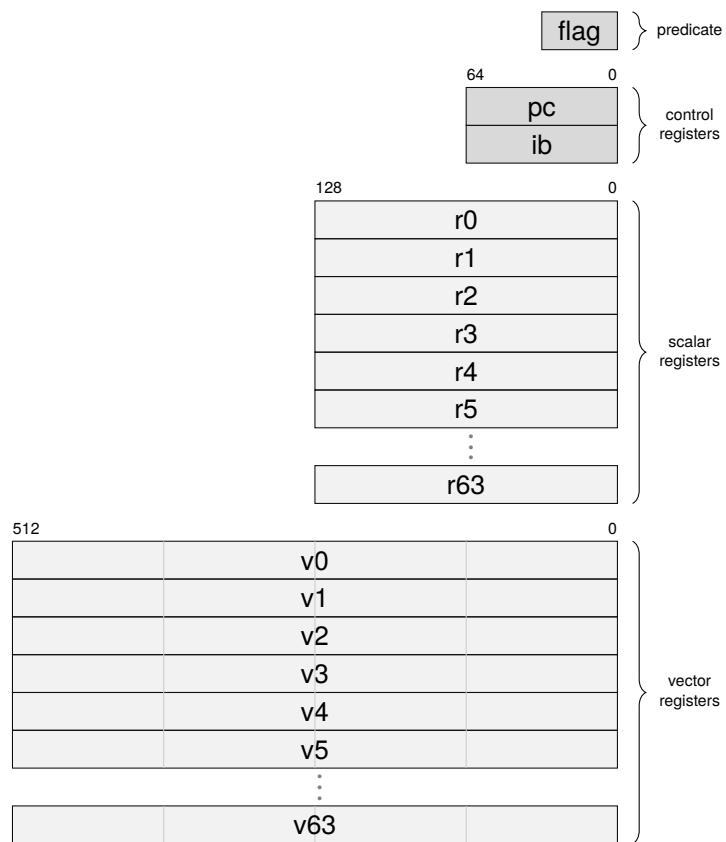

### 1.6.4. *vector-min* architectural profile

the register state accessible by the *vector-min* architectural profile is comprised of:

- 1-bit predicate register (*flag*).

- 64-bit *program counter* register (aligned to 2 bytes).

- 64-bit *immediate base* register (aligned to 64 bytes).

- $64 \times 128$ -bit scalar registers ( $r0 — r63$ ).

- $64 \times 512$ -bit vector registers ( $v0 — v63$ ).

the following diagram shows the *vector-min* architectural profile register state:

Figure 1.15.: *vector-min* architectural profile register state.

## 1. Architecture

### 1.6.5. *vector-max* architectural profile

the register state accessible by the *vector-max* architectural profile is comprised of:

- 1-bit predicate register (*flag*).

- 64-bit *program counter* register (aligned to 2 bytes).

- 64-bit *immediate base* register (aligned to 64 bytes).

- $64 \times 128$ -bit scalar registers ( $r0 — r63$ ).

- $64 \times 4096$ -bit vector registers ( $v0 — v63$ ).

the following diagram shows the *vector-max* architectural profile register state:

Figure 1.16.: *vector-max* architectural profile register state.

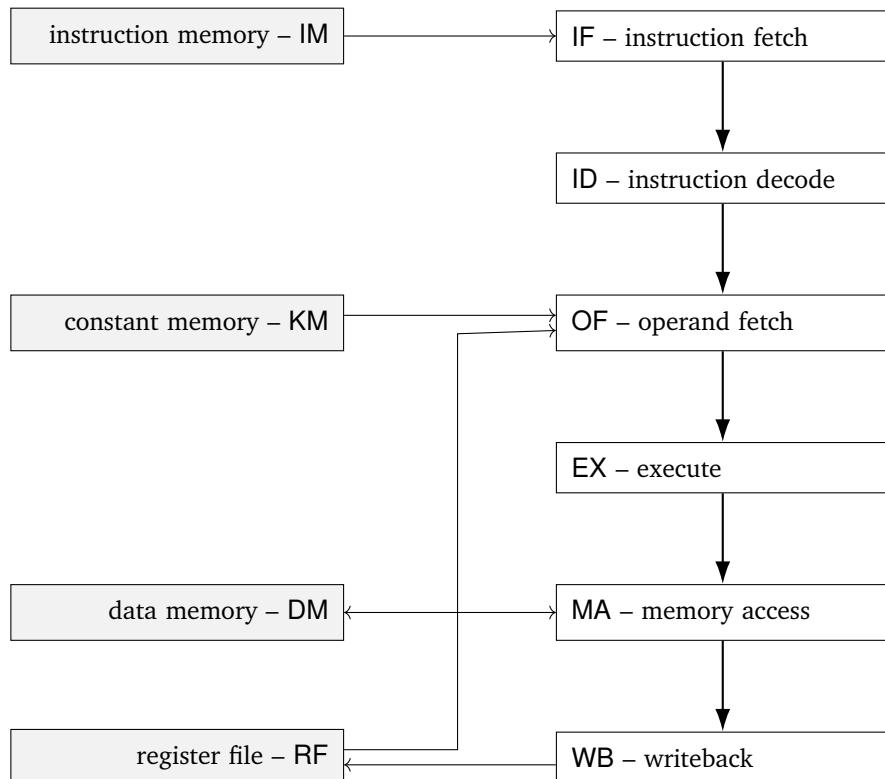

## 1.7. Example pipeline

an illustrative micro-architecture is proposed based on the classic 5-stage RISC micro-architecture [10] with the addition of an *operand fetch* stage and a *constant memory* port. this revised 6-stage micro-architecture is composed of the following pipeline stages:

- IF — *instruction fetch*: reads instructions from memory into a fetch buffer.

- ID — *instruction decode*: decodes instruction length, opcode, and operands.

- OF — *operand fetch*: reads operands from register file and constant memory.

- EX — *execute*: performs logical operations or arithmetic on the operands.

- MA — *memory access*: loads data from or stores data to memory.

- WB — *writeback*: writes results back to the register file.

a simplified micro-architecture using those pipeline stages might look like this: this example omits hazard detection and forwarding logic for the sake of simplicity.

Figure 1.17.: sample 6-stage micro-architecture with support for constant memory.

# 2. System

## 2.1. User-level registers

the architecture provides several user-level status and control registers for floating-point status and control, clock time, clock frequency, thread address and domain.

user-level status and control registers can be read and written using the `sysread`, `syswrite`, `sysset`, and `sysclear` instructions. user-level status and control registers are available in contexts where their associated bit is enabled in `scontrol`.

### **user-level registers**

the following table lists the user-level registers:

| no.                                  | name      | description            |

|--------------------------------------|-----------|------------------------|

| <b>floating-point unit registers</b> |           |                        |

| 0x00                                 | fstatus   | floating-point status  |

| 0x01                                 | fpcontrol | floating-point control |

| <b>clock and frequency registers</b> |           |                        |

| 0x02                                 | ctime     | clock time             |

| 0x03                                 | cfreq     | clock frequency        |

| <b>thread address registers</b>      |           |                        |

| 0x04                                 | addr      | user thread address    |

| 0x05                                 | domain    | user thread domain     |

Table 2.1.: user-level registers

### 2.1.1. floating-point unit registers

the section describes the user-level floating-point unit registers.

#### floating-point status (fpstatus)

fpstatus is a read-only register containing status information for floating-point operations. the Z, O, U, X, and I fields contain accrued floating-point exceptions. this register is visible if scontrol.F is enabled.

|  |  |  |  |  |  | 4 | 3 | 2 | 1 | 0 |

|--|--|--|--|--|--|---|---|---|---|---|

|  |  |  |  |  |  | Z | O | U | X | I |

| no.    | name | description       |

|--------|------|-------------------|

| 1 << 0 | I    | invalid operation |

| 1 << 1 | X    | inexact result    |

| 1 << 2 | U    | numeric underflow |

| 1 << 3 | O    | numeric overflow  |

| 1 << 4 | Z    | divide by zero    |

Table 2.2.: floating-point status flags

#### floating-point control (fpcontrol)

fpcontrol is a read-write register containing control information for floating-point operations. the RM field contains the current floating-point rounding mode. the Z field enables *flush-to-zero* and *denormals-are-zero*. the N field enables *not-strict-ieee754*, allowing *fused-multiply-add* and other optimizations that may affect precision. this register is visible if scontrol.F is enabled.

|  |  |  |  |  | 3  | 2 | 1 | 0 |

|--|--|--|--|--|----|---|---|---|

|  |  |  |  |  | RM | N | Z |   |

| no.    | name | description                                        |

|--------|------|----------------------------------------------------|

| 1 << 0 | Z    | <i>flush-to-zero</i> and <i>denormals-are-zero</i> |

| 1 << 1 | N    | <i>not-strict-ieee754</i>                          |

Table 2.3.: floating-point control flags

| no. | name | description                     |

|-----|------|---------------------------------|

| 0   | RN   | round to nearest (even)         |

| 1   | RD   | round down (towards $-\infty$ ) |

| 2   | RU   | round up (towards $+\infty$ )   |

| 3   | RZ   | round towards zero (truncate)   |

Table 2.4.: floating-point control round mode field

### 2.1.2. clock and frequency registers

the section describes the user-level clock and frequency registers.

#### clock time (ctime)

ctime is a read-only register containing the wall-clock tick counter since power on in clock tick units denoted by cfreq. this register is visible if scontrol.T is enabled.

|                   |  |   |

|-------------------|--|---|

| 63                |  | 0 |

| <i>clock time</i> |  |   |

#### clock frequency (cfreq)

cfreq is a read-only register containing the wall-clock tick interval in picoseconds;  $\frac{10^{12}}{f}$  where  $f$  is the frequency in Hertz (Hz). this register is visible if scontrol.T is enabled.

|                        |  |   |

|------------------------|--|---|

| 63                     |  | 0 |

| <i>clock frequency</i> |  |   |

### 2.1.3. thread address registers

the section describes the user-level thread address registers.

#### thread address (addr)

addr is a read-only register containing an alias of the unique system-wide topological address for this thread from saddr. this register is visible if scontrol.D is enabled.

|                       |  |   |

|-----------------------|--|---|

| 63 62                 |  | 0 |

| <i>thread address</i> |  |   |

#### thread domain (domain)

domain is a read-only register containing an alias of the system-wide domain address for this thread from sdomain. this register is visible if scontrol.D is enabled.

|                      |  |   |

|----------------------|--|---|

| 63 62                |  | 0 |

| <i>thread domain</i> |  |   |

## 2.2. System registers

the architecture provides several privileged status and control registers for trap handling, system configuration, address translation, timers, interrupts, and debugging.

privileged system-level status and control registers can be read and written using the `sysread`, `syswrite`, `sysset`, and `sysclear` instructions. privileged system registers are accessible from executable pages with system or physical address spaces.

### privileged registers

the following table lists the privileged trap, system, debug and machine registers:

| no.                                | name     | description                    |

|------------------------------------|----------|--------------------------------|

| <b>privileged trap registers</b>   |          |                                |

| 0x10                               | tstatus  | trap status                    |

| 0x11                               | tcontrol | trap control                   |

| 0x12                               | tscratch | trap scratch                   |

| 0x13                               | tvalue   | trap value                     |

| 0x14                               | tcause   | trap cause                     |

| 0x15                               | tack     | trap acknowledge               |

| 0x16                               | tepc     | trap exception program counter |

| 0x17                               | teib     | trap exception immediate base  |

| 0x18                               | thpc     | trap handler program counter   |

| 0x19                               | thib     | trap handler immediate base    |

| <b>privileged system registers</b> |          |                                |

| 0x21                               | scontrol | system control                 |

| 0x22                               | sfeature | system feature                 |

| 0x23                               | sversion | system version                 |

| 0x24                               | sprt     | system page table root         |

| 0x25                               | saddr    | system thread address          |

| 0x26                               | sdomain  | system thread domain           |

| 0x27                               | starget  | system target address          |

| 0x28                               | smessage | system target message          |

| 0x29                               | stimer   | system deadline timer          |

| 0x2a                               | sie      | system interrupt enable        |

| 0x2b                               | sip      | system interrupt pending       |

| <b>privileged debug registers</b>  |          |                                |

| 0x30                               | dstatus  | debug status                   |

| 0x32                               | dcycle   | debug cycle counter            |

| 0x33                               | dinst    | debug instruction counter      |

| 0x34                               | dstop    | debug stop instruction         |

| 0x35                               | dfetch   | debug monitor fetch address    |

| 0x36                               | dread    | debug monitor read address     |

| 0x37                               | dwrite   | debug monitor write address    |

Table 2.5.: privileged registers

### 2.2.1. privileged trap registers

the section describes the privileged trap registers.

#### trap status (tstatus)

tstatus is a read-only register containing trap status. the T field indicates whether a timer interrupt is pending. the V field indicates whether a virtual interrupt is pending.

|  |   |   |

|--|---|---|

|  | 1 | 0 |

|  | V | T |

| no.    | name | description               |

|--------|------|---------------------------|

| 1 << 0 | T    | timer interrupt pending   |

| 1 << 1 | V    | virtual interrupt pending |

Table 2.6.: trap status fields

#### trap control (tcontrol)

tcontrol is a read-write register containing control bits. the I field is read-write and controls whether system interrupts are enabled.

|  |   |  |

|--|---|--|

|  | 0 |  |

|  | I |  |

| no.    | name | description             |

|--------|------|-------------------------|

| 1 << 0 | I    | system interrupt enable |

Table 2.7.: trap control fields

#### trap scratch (tscratch)

tscratch is a read-write save register for use during trap handling.

|  |                      |   |  |

|--|----------------------|---|--|

|  | 63                   | 0 |  |

|  | <i>scratch value</i> |   |  |

## 2. System

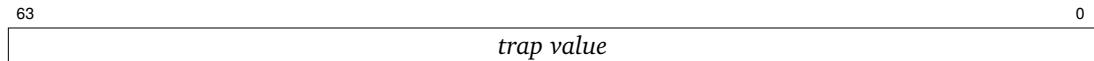

### trap value (tvalue)

tvalue is a read-only register containing the identity of the trap and may contain:

- the faulting instruction word for *break* and *illegal instruction exceptions*.

- the faulting address for *misaligned*, *access* and *page faults*.

- the message value for *virtual interrupts*.

- the system clock time for *timer interrupts*.

### trap cause (tcause)

tcause is a read-only register that contains the cause of the current trap.

| no.                      | name                | description                   |

|--------------------------|---------------------|-------------------------------|

| <b>system exceptions</b> |                     |                               |

| 1                        | break-instruction   | break instruction exception   |

| 2                        | illegal-instruction | illegal instruction exception |

| 3                        | debug-monitor       | debug monitor exception       |

| 4                        | misaligned-fetch    | fetch misaligned              |

| 5                        | misaligned-load     | load misaligned               |

| 6                        | misaligned-store    | store misaligned              |

| 7                        | access-fault-fetch  | fetch access fault            |

| 8                        | access-fault-load   | load access fault             |

| 9                        | access-fault-store  | store access fault            |

| 10                       | page-fault-fetch    | fetch page fault              |

| 11                       | page-fault-load     | load page fault               |

| 12                       | page-fault-store    | store page fault              |

| 13                       | capability-fault    | capability fault              |

| 14                       | domain-fault        | domain fault                  |

| 15                       | machine-fault       | machine fault                 |

| <b>system interrupts</b> |                     |                               |

| 30                       | timer-interrupt     | timer interrupt               |

| 31                       | virtual-interrupt   | virtual interrupt             |

| 32...63                  | interrupt-n         | interrupt pins 0 – 31         |

Table 2.8.: trap causes

## 2. System

### trap acknowledge (tack)

tack is a write-only register where the trap cause is written to acknowledge the trap so that interrupts are not delivered while state is being saved, and for double-faults to be detected.

|       |   |   |

|-------|---|---|

|       | 5 | 0 |

| cause |   |   |

### trap exception program counter (tepc)

tepc is a read-only register which contains the *program counter* address before the trap.

|                 |    |   |

|-----------------|----|---|

|                 | 63 | 0 |

| program counter |    |   |

### trap exception immediate base (teib)

teib is a read-only register which contains the *immediate base* address before the trap.

|                |    |   |

|----------------|----|---|

|                | 63 | 0 |

| immediate base |    |   |

### trap handler program counter (thpc)

thpc is a read-write register containing the address of the system trap handler routine.

|                 |    |   |

|-----------------|----|---|

|                 | 63 | 0 |

| program counter |    |   |

### trap handler immediate base (thib)

thib is a read-write register containing the address of the system trap handler constants.

|                |    |   |

|----------------|----|---|

|                | 63 | 0 |

| immediate base |    |   |

### 2.2.2. privileged system registers

the section describes the privileged system registers.

#### system control (scontrol)

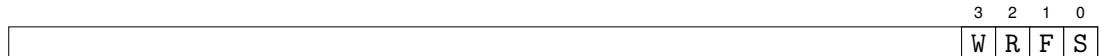

scontrol is a read-write register containing system control bits.

|  |  |  |  |  |  | 4 | 3 | 2 | 1 | 0 |

|--|--|--|--|--|--|---|---|---|---|---|

|  |  |  |  |  |  | E | A | D | T | F |

| no.    | name | description                                |

|--------|------|--------------------------------------------|

| 1 << 0 | F    | floating-point unit enabled                |

| 1 << 1 | T    | user clock and frequency enabled           |

| 1 << 2 | D    | user address and domain enabled            |

| 1 << 3 | A    | user address space access disable enabled  |

| 1 << 4 | E    | user address space execute disable enabled |

Table 2.9.: system control fields

#### system feature (sfeature)

sfeature is a read-only register containing system feature bits.

|  |  |  |  |  |  | 4 | 3 | 2 | 1 | 0 |

|--|--|--|--|--|--|---|---|---|---|---|

|  |  |  |  |  |  | E | A | D | T | F |

| no.    | name | description                                |

|--------|------|--------------------------------------------|

| 1 << 0 | F    | floating-point unit feature                |

| 1 << 1 | T    | user clock and frequency feature           |

| 1 << 2 | D    | user address and domain feature            |

| 1 << 3 | A    | user address space access disable feature  |

| 1 << 4 | E    | user address space execute disable feature |

Table 2.10.: system feature fields

## 2. System

### system version (sversion)

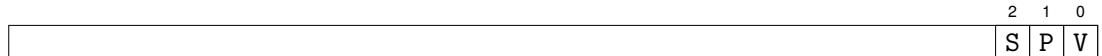

sversion is a read-only register containing a specification version number described by its *major*, *minor*, and *patch* fields. the allowable values are specified in the following table.

|  | 23 | 16 | 15 | 8                   | 7            | 0            |

|--|----|----|----|---------------------|--------------|--------------|

|  |    |    |    | <i>major</i>        | <i>minor</i> | <i>patch</i> |

|  |    |    |    | 0                   | 6            | 0            |

|  |    |    |    | pre-release current |              |              |

Table 2.11.: system version values

### system page table root (splt)

splt is a read-write register containing the page table root physical address for address translation on this thread. the *ASID* field contains the address space identifier for this thread.

| 63                   | 48 47                       | 12 11       | 0 |

|----------------------|-----------------------------|-------------|---|

| <i>sign extended</i> | <i>physical page number</i> | <i>ASID</i> |   |

### system thread address (saddr)

saddr is a read-only register containing the unique system-wide topological address for this thread. the system-wide topological address is used as a target for inter-thread virtual interrupts. this address is uniquely assigned during system initialization.

| 63 62 | 0 | thread address | 0 |

|-------|---|----------------|---|

| 0     |   |                |   |

### system thread domain (sdomain)

sdomain is a read-only register containing the system-wide domain address for this thread. the system-wide domain address is used as a target for inter-thread virtual interrupts. this address can alias. this address is assigned during context switching.

| 63 62 | 1 | thread domain | 0 |

|-------|---|---------------|---|

| 1     |   |               |   |

## 2. System

### system target address (starget)

starget is a read-write register containing the system-wide target address of a thread to send a virtual interrupt. all-zeros is the *boot service processor*. all-ones is the *broadcast address*. zero in the A field is a *topological address*. one in the A field is a *domain address*.

|    |    |                |   |

|----|----|----------------|---|

| 63 | 62 |                | 0 |

| A  |    | target address |   |

### system target message (smessage)

smessage is a write-only register that causes an edge-triggered virtual interrupt to be queued to the thread set in starget. virtual interrupts are marked pending in the V field of the tstatus register for the target thread.

|    |               |   |

|----|---------------|---|

| 63 |               | 0 |

|    | message value |   |

### system deadline timer (stimer)

stimer is a read-write register containing the deadline timer for this thread. when the system clock reaches the value in the register, a *timer interrupt* is triggered. timer interrupts are marked pending in the T field of the tstatus register.

|    |            |   |

|----|------------|---|

| 63 |            | 0 |

|    | clock time |   |

### system interrupt enable (sie)

sie is a read-write register that contains interrupt enable flags for 32 wired interrupt pins.

|    |                       |   |

|----|-----------------------|---|

| 31 |                       | 0 |

|    | interrupt enable 0-31 |   |

### system interrupt pending (sip)

sip is a read-only register that contains interrupt pending flags for 32 wired interrupt pins.

|    |                        |   |

|----|------------------------|---|

| 31 |                        | 0 |

|    | interrupt pending 0-31 |   |

### 2.2.3. privileged debug registers

the section describes the privileged debug registers.

#### debug status (dstatus)

dstatus is a read-only register containing status bits for debug monitor exceptions.

| no.    | name | description           |

|--------|------|-----------------------|

| 1 << 0 | S    | stopping instruction  |

| 1 << 1 | F    | fetch monitor address |

| 1 << 2 | R    | load monitor address  |

| 1 << 3 | W    | store monitor address |

Table 2.12.: debug status fields

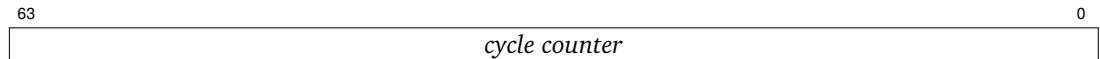

#### debug cycle counter (dcycle)

dcycle is a read-only register containing the number of cycles retired since power on.

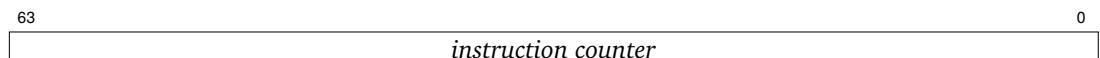

#### debug instruction counter (dinst)

dinst is a read-only register containing the number of instructions retired since power on.

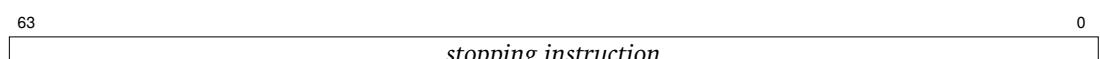

#### debug stop instruction (dstop)

dstop is a read-write register containing an instruction number to halt execution on and raise a *debug monitor exception*.

## 2. System

### **debug monitor fetch address (dfetch)**

dfetch is a read-write register containing a memory fetch address to monitor for and halt execution on and raise a *debug monitor exception* for a matching memory fetch address.

|                      |   |

|----------------------|---|

| 63                   | 0 |

| <i>fetch address</i> |   |

### **debug monitor read address (dread)**

dread is a read-write register containing the memory load address to monitor for and halt execution on and raise a *debug monitor exception* for a matching memory load address.

|                     |   |

|---------------------|---|

| 63                  | 0 |

| <i>read address</i> |   |

### **debug monitor write address (dwrite)**

dwrite is a read-write register containing the memory store address to monitor for and halt execution on and raise a *debug monitor exception* for a matching memory store address.

|                      |   |

|----------------------|---|

| 63                   | 0 |

| <i>write address</i> |   |

## 2.3. Capability extension

the architecture provides an optional capabilities extension that provides a capability check for permissions and capabilities enabled by *page table colors* in page table entries. color permissions mask page table permissions based on *page table color*. color capabilities restrict access to system, domain, capability and machine registers based on *page table color*.

the following tables list the privileged capability system parameters:

| name        | description                        |

|-------------|------------------------------------|

| <i>ncol</i> | the number of architectural colors |

Table 2.13.: capability parameters

### capability registers

the following tables list the privileged capability system registers:

| no.                                    | name                      | description                    | depends |

|----------------------------------------|---------------------------|--------------------------------|---------|

| <b>capability control registers</b>    |                           |                                |         |

| 0x41                                   | ccontrol                  | capability control             |         |

| <b>capability permission registers</b> |                           |                                |         |

| 0x43                                   | colorread                 | color read permissions         |         |

| 0x44                                   | colorwrite                | color write permissions        |         |

| 0x45                                   | colorexec                 | color exec permissions         |         |

| <b>capability role registers</b>       |                           |                                |         |

| 0x46                                   | colorsys                  | color system role              |         |

| 0x47                                   | colordom                  | color domain role              | domain  |

| 0x48                                   | colorcap                  | color capability role          |         |

| 0x49                                   | colormac                  | color machine role             | machine |

| <b>capability matrix registers</b>     |                           |                                |         |

| 0x100...0x10f                          | colormatread[ <i>n</i> ]  | color matrix read permissions  |         |

| 0x200...0x20f                          | colormatwrite[ <i>n</i> ] | color matrix write permissions |         |

| 0x300...0x30f                          | colormatexec[ <i>n</i> ]  | color matrix exec permissions  |         |

Table 2.14.: capability registers

### 2.3.1. capability control registers

this section describes the *capability control registers* which enable the capability extension.

#### capability control (ccontrol)

ccontrol is a read-write register containing capability control bits.

| no.    | name | description             |

|--------|------|-------------------------|

| 1 << 0 | C    | capability check enable |

Table 2.15.: color control fields

### 2.3.2. capability permission registers

this section describes the *capability permission registers* which define *page table color* permission masks for page table entries. when ccontrol.C is set, the *capability permission registers* are combined with page table permissions to limit maximum *read*, *write*, or *execute* permission based on page table color.

#### color read permission (colorread)

colorread is a read-write register containing an array of *ncol* bits containing read permissions for *color-x*, used to check loads from pages with a matching page table color.

#### color write permission (colorwrite)

colorwrite is a read-write register containing an array of *ncol* bits containing write permissions for *color-x*, used to check stores to pages with a matching page table color.

#### color exec permission (colorexec)

colorexec is a read-write register containing an array of *ncol* bits containing execute permissions for *color-x*, used to check execution in pages with a matching page table color.

### 2.3.3. capability role registers

this section describes the *capability role registers*. the *capability role registers* describe access to privileged system registers and instructions based on *page table color*. when `ccontrol.C` is set, privileged system registers and instructions will cause capability traps for illegal accesses. system registers and instructions are restricted based on the following roles: *system*, *domain*, *capability* and *machine*.

#### color system role (colorsys)

colorsys is a read-write register containing an array of *ncol* bits containing system role for *color-x*, used to check access to privileged trap registers, privileged system registers and privileged debug registers from executable pages with a matching page table color.

|             |                    |

|-------------|--------------------|

| <i>ncol</i> | 0                  |

|             | <i>system role</i> |

#### color domain role (colordom)

colordom is a read-write register containing an array of *ncol* bits containing domain role for *color-x* that are used to check access to privileged domain registers from executable pages with a matching page table color.

|             |                    |

|-------------|--------------------|

| <i>ncol</i> | 0                  |

|             | <i>domain role</i> |

#### color capability role (colorcap)

colorcap is a read-write register containing an array of *ncol* bits containing capability role for *color-x* that are used to check access to privileged capability registers from executable pages with a matching page table color.

|             |                        |

|-------------|------------------------|

| <i>ncol</i> | 0                      |

|             | <i>capability role</i> |

#### color machine role (colormac)

colormac is a read-write register containing an array of *ncol* bits containing machine role for *color-x* that are used to check access to privileged machine registers from executable pages with a matching page table color.

|             |                     |

|-------------|---------------------|

| <i>ncol</i> | 0                   |

|             | <i>machine role</i> |

### 2.3.4. capability matrix registers

this section describes the color matrix registers. the *capability matrix registers* are permission registers that protect access to memory based on a combination of *source* and *destination* page table color and *read*, *write*, or *execute* permissions. when `ccontrol.C` is set, memory accesses and branches to memory addresses in pages with matching *source* and *destination* page table colors, and wider permissions, will cause capability traps.

#### color matrix read permissions (colormatread[ncol])

`colormatread[ncol]` are *ncol* read-write registers containing an array of *ncol* bits with read permissions, used to check loads from executable pages with a matching register *page table color* to memory addresses in memory pages with a matching *page table color* index.

|  |             |                   |   |

|--|-------------|-------------------|---|

|  | <i>ncol</i> |                   | 0 |

|  |             | <i>read perms</i> |   |

#### color matrix write permissions (colormatwrite[ncol])

`colormatwrite[ncol]` are *ncol* read-write registers containing an array of *ncol* bits with write permissions, used to check stores from executable pages with a matching register *page table color* to memory addresses in memory pages with a matching *page table color* index.

|  |             |                    |   |

|--|-------------|--------------------|---|

|  | <i>ncol</i> |                    | 0 |

|  |             | <i>write perms</i> |   |

#### color matrix exec permissions (colormatexec[ncol])

`colormatexec[ncol]` are *ncol* read-write registers containing an array of *ncol* bits with exec permissions, used to check branches from executable pages with a matching register *page table color* to branch addresses in executable pages with a matching *page table color* index.

|  |             |                   |   |

|--|-------------|-------------------|---|

|  | <i>ncol</i> |                   | 0 |

|  |             | <i>exec perms</i> |   |

## 2.4. Domain extension

the architecture provides an optional domain [3] extension for virtual machines. the extension adds registers for virtual domain addresses, trap routing, page translation, and context switching for system traps, domain traps, capability traps and machine traps.

the following tables list the privileged domain system parameters:

| name        | description                         |

|-------------|-------------------------------------|

| <i>ndom</i> | the number of architectural domains |

Table 2.16.: domain parameters

### domain registers

the following tables list the privileged domain system registers:

| no.                             | name         | description                         | depends    |

|---------------------------------|--------------|-------------------------------------|------------|

| <b>domain control registers</b> |              |                                     |            |

| 0x51                            | domcontrol   | domain control                      |            |

| 0x53                            | domlast      | domain number last                  |            |

| 0x54                            | domcurr      | domain number current               |            |

| 0x55                            | domnext      | domain number next                  |            |

| <b>domain routing registers</b> |              |                                     |            |

| 0x500...0x50f                   | dommatrix[n] | domain matrix                       |            |

| 0x600...0x60f                   | domsys[n]    | domain system default domain        |            |

| 0x700...0x70f                   | domdom[n]    | domain domain default domain        |            |

| 0x800...0x80f                   | domcap[n]    | domain capability default domain    | capability |

| 0x900...0x90f                   | dommac[n]    | domain machine default domain       | machine    |

| <b>domain context registers</b> |              |                                     |            |

| 0xa00...0xa0f                   | domaddr[n]   | domain address                      |            |

| 0xb00...0xb0f                   | domptr[n]    | domain page table root              |            |

| 0xc00...0xc0f                   | domthpc[n]   | domain trap handler program counter |            |

| 0xd00...0xd0f                   | domthib[n]   | domain trap handler immediate base  |            |

Table 2.17.: domain registers

### 2.4.1. domain control registers

this section describes the *domain control registers* which enable the domain extension and provide access to last and current domain number and control the next domain number.

#### domain control (domcontrol)

domcontrol is a read-write register containing domain control bits.

| no.    | name | description            |

|--------|------|------------------------|

| 1 << 0 | V    | virtual domains enable |

Table 2.18.: domain control fields

#### domain number last (domlast)

domlast is a read-only register containing the domain number of the last domain.

#### domain number current (domcurr)

domcurr is a read-only register containing the domain number of the current domain.

#### domain number next (domnext)

domnext is a read-write register containing the domain number of the next domain.

### 2.4.2. domain routing registers

this section describes the *domain routing registers* that control valid domain transitions and routing for context switching of system, domain, capability and machine traps.

#### domain matrix (dommatrix[ndom])

dommatrix[ndom] are *ndom* read-write registers containing a matrix of the domains that the current domain is allowed to transition to as the next domain.

| ndom | 0               |

|------|-----------------|

|      | allowed domains |

#### domain system default domain (domsys[ndom])

domsys[ndom] are *ndom* read-write registers containing the domain number of the domain that system traps are routed to.

| $\log_2(\text{ndom})$ | 0      |

|-----------------------|--------|

|                       | domain |

#### domain domain default domain (domdom[ndom])

domdom[ndom] are *ndom* read-write registers containing the domain number of the domain that domain traps are routed to.

| $\log_2(\text{ndom})$ | 0      |

|-----------------------|--------|

|                       | domain |

#### domain capability default domain (domcap[ndom])

domcap[ndom] are *ndom* read-write registers containing the domain number of the domain that capability traps are routed to.

| $\log_2(\text{ndom})$ | 0      |

|-----------------------|--------|

|                       | domain |

#### domain machine default domain (dommac[ndom])

dommac[ndom] are *ndom* read-write registers containing the domain number of the domain that machine traps are routed to.

| $\log_2(\text{ndom})$ | 0      |

|-----------------------|--------|

|                       | domain |

### 2.4.3. domain context registers

this section describes the *domain context registers* that control virtual interrupt routing, page translation and trap entry functions for domain context switching.

#### domain address (domaddr[ndom])

domaddr[ndom] are *ndom* read-write registers containing an array of the domain addresses associated with each domain. domain context switches copy the value for the target domain into **sdomain** to enable virtual interrupt delivery.

|       |   |                |   |

|-------|---|----------------|---|

| 63 62 | 1 | domain address | 0 |

|-------|---|----------------|---|

#### domain page table root (domptr[ndom])

domptr[ndom] are *ndom* read-write registers containing an array of the page table root physical addresses for address translation in each domain. domain context switches copy the value for the target domain into **sprt** to enable address translation.

|    |       |               |       |                      |   |      |

|----|-------|---------------|-------|----------------------|---|------|

| 63 | 48 47 | sign extended | 12 11 | physical page number | 0 | ASID |

|----|-------|---------------|-------|----------------------|---|------|